En 2012, une révolution silencieuse se prépare. Le mode de fabrication des transistors que nous utilisons par milliards chaque jour va subir des aménagements conséquents afin de préserver la cadence infernale de miniaturisation initiée il y a 40 ans, avec le 4004. Petit survol de ce qui attend les futures puces.

Ah, la « loi de Moore »… si tellement de scientifiques de n’arrachaient pas les cheveux afin de la respecter, la vie de la plupart des geeks serait d’un morose… Elle indique que le nombre de transistors dont sont constitués les circuits intégrés double tous les deux ans (ou tous les 18 mois selon les versions). En fait de loi, c’est plutôt une constatation empirique, et surtout un objectif que l’incroyable ingéniosité des scientifiques a réussi à atteindre ces 40 dernières années. Pourtant, c’est de plus en plus difficile. L’année prochaine verra l’introduction de changements majeurs dans la manière de fabriquer les composants. Deux techniques vont devoir se mesurer et, à travers elles, les constructeurs vont se battre pour garder leur leadership ou, pourquoi pas, conquérir une nouvelle suprématie. Avant de décrire les nouvelles techniques, on va tout de même passer un peu de temps à décrire la manière dont fonctionne les transistors de vos appareils chéris et comment ils sont fabriqués.

Les Transistors MOSFET

Je ne vous surprendrais pas en vous révélant que le CPU de votre tablette est un circuit intégré dont le composant principal est le transistor. C’est une sorte de minuscule interrupteur, qui ne fait que quelques nanomètres (un millionième de millimètre) de large. Ces transistors sont des MOSFET c’est-à-dire « Metal Oxyde Semiconductor Field Effect Transistor », ouf ! Reprenons calmement. Les semi-conducteurs sont des matériaux isolants… en général, mais qui peuvent se comporter comme des conducteurs si on se montre persuasif. En fait, la mobilité des électrons dans un semi-conducteur est suffisante pour que, si on en amasse suffisamment dans une certaine zone, celle-ci fasse un « pont » conducteur. Pour attirer les électrons, on utilise un champ électrique, d’où le nom de transistor à « effet de champs » (FET pour Field Effect Transistor).

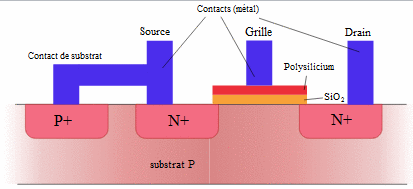

Très schématiquement, ils sont constitués de 3 composantes : la source, la grille et le drain déposés sur un substrat de silicium. Il y a un « canal » isolant entre la source et le drain. Le courant passe, ou pas, entre la source et le drain en fonction de la tension appliquée sur la grille qui génère le fameux champ électrique. Si le champ attire suffisamment d’électrons dans le canal, le courant passe et l’interrupteur est ouvert, sinon il est fermé. Source, grille et drain sont métalliques (conducteur) et entre la source et le drain, le canal est un isolant fait d’oxyde de silicium, d’où le MOS pour Metal / Oxyde Semiconductor.

C’est la taille de ces composants qui doit donc être réduite tous les deux ans pour coller à la loi de Moore. Au début, ce n’était pas trop dur, de 1974 aux années 1990, les MOSFET se sont réduits au rythme des différents procédés de photolithographie en suivant bien sagement la loi de Moore. Puis les choses se sont accélérées, les transistors se sont réduits plus vite que le voltage. Or, avec un voltage relativement élevé, il passe un peu de courant à travers le transistor même si celui-ci est fermé: c’est une fuite. Les courants de fuite devinrent significatifs. Dans les années 2000, ils approchèrent dangereusement le voltage de contrôle (celui appliqué pour basculer le transistor). Funeste époque pour Intel, dont le Pentium 4 a beaucoup souffert de ce syndrome.

En 2007, à l’aube du passage au 45nm, Intel remplace le dioxyde de silicium du canal par de l’oxyde de hafnium, un « high-k dielectric ». Cela signifie juste que c’est un meilleur isolant. Mais aujourd’hui, à l’approche des 20nm, même le régime spécial k n’est plus suffisant et il est temps de changer un peu plus radicalement la manière de fabriquer les transistors. Deux approches principales peuvent être suivies.

Ultra Thin Body Silicon over Insulator

Cette méthode est la moins médiatisée des deux, pourtant, elle possède des qualités. Comme l’indique son nom à rallonge pour ceux qui parlent la langue des Beatles, les transistors « UTB SOI » remplacent le substrat par une fine couche de silicium posée sur un isolant.

Pourquoi faire ça ? Et bien parce que les courants de fuites ont tendance à passer par la profondeur du substrat (qui est semi-conducteur), loin de la grille, dont le champ décroit rapidement. Du coup, en amincissant le substrat semi-conducteur au maximum, on évite que les électrons ne prennent la tangente.

Les UTB SOI sont ainsi assez proches des transistors standards, les chaines de montage actuelles ne devront pas être modifiées en profondeur. Cela économise des sommes colossales tant les usines sont complexes, il y a près de 400 étapes dans la création d’un wafer. Seulement, leur fabrication n’est pas simple pour autant, la couche mince doit être … vraiment très mince et surtout, très homogène, à 0.5 nm près sur un wafer de 30cm de diamètre ! Une fois ces défis relevés (déjà fait par SOITEC) et industrialisés, les UTB devraient permettre d’aller jusqu’à des finesses de 5nm.

FinFET alias “TriGate”

Les transistors FinFET (aucun rapport avec Bobba Fett) sont encore plus efficaces et encore plus compliqués à produire. « Fin » peut se traduire par « ailette ». Ici, le transistor est en quelque sorte pivoté sur un côté. La source et le drain forment une « ailette » très fine (10nm ou moins) surélevée au-dessus d’un substrat isolant, et la grille l’entoure sur ses trois côtés restants. Ces transistors sont ainsi « en relief » et Intel les qualifie de transistors « 3D » ou encore de TriGate. En entourant complètement le canal, la grille possède un contrôle quasi complet sur ce qui s’y passe, les courants de fuites sont éliminés et la consommation des composants est significativement diminuée.

Intel, qui le premier a réussi à industrialiser le processus de fabrication FinFET, avait beaucoup communiqué sur ses transistors et avait même produit une vidéo « documentaire »:

[youtube YIkMaQJSyP8]

Pour fabriquer des transistors TriGate, il faut néanmoins bien réussir ses ailettes: elles doivent typiquement être hautes d’une dizaine de nanomètres, larges d’une vingtaine et ne pas dévier de plus d’un nanomètre sur les 30cm de diamètre d’un wafer. Et cela pendant toutes les (nombreuses) étapes de fabrication !

FinFET et UTB SoI ont chacun leurs avantages et leurs inconvénients. Les FinFET sont un peu plus efficaces, mais plus difficiles à produire. La fabrication des UTB SOI peut être plus vite mise en œuvre, mais risque de saturer vers les 7nm. Les FinFET devraient pouvoir aller plus loin (3nm ?), mais coutent plus cher…

2012 : l’apocalypse la transition

Les grands constructeurs : TSMC, IBM, Samsung etc., font de toute façon des recherches sur les deux procédés. Il est encore bien difficile de prédire lequel s’imposera. En mars 2012, la bataille sera lancée avec la prochaine génération de CPU d’Intel : Ivy Bridge.

Ivy Bridge est la même architecture que l’actuelle Sandy Bridge mais gravée en 22nm au lieu de 32nm. Or, pour atteindre ces dimensions, Intel doit sauter le pas. Malgré la difficulté, son choix s’est porté sur les FinFET. Intel est pour le moment le seul constructeur à maîtriser la fabrication industrielle du FinFET en 22nm. Cela représente une avance de plusieurs années sur la concurrence. Une avance décisive qui pourrait bien se révéler d’une importance stratégique sur un marché en évolution rapide.

Le point faible d’Intel vis-à-vis d’ARM est la consommation, sa maîtrise des processus de fabrication lui permettra peut-être de combler son retard. Par rapport à un transistor à 32nm, Intel annonce 37% de performance supplémentaire, ou autant d’économies d’énergies. La ligne Atom de la marque devrait se rapprocher de plus en plus d’un SoC en 2012 et passer en 32nm au début de l’année. Entre les CULV 22nm, les prochains Atom et les très mystérieux Saltwell destinés au tablettes, les progrès majeurs d’Intel dans le domaine de l’énergie le rapproche de ses actuels ennemis mortels : les processeurs ARM.

La consommation énergétique est le nouveau cheval de bataille d’Intel, après Ivy Bridge, c’est Haswell qui prendra le relai en 2013, toujours en Trigate 22nm. Avec cette génération, l’objectif d’Intel est de réduire de 30% la consommation par rapport à Ivy Bridge. Avec des TDP de 15W ou moins, partie graphique intégrée, Intel vise des ultrabooks censés offrir des autonomies records, et pourquoi pas les tablettes Windows 8 ? Enfin, avec le « die shrink » d’Haswell en 2014, Intel promet des portables pouvant tenir une semaine entière sans être rechargés.

Intel réussira-t-il à dominer le marché des tablettes comme il domine celui des ordinateurs grâce à ses transistors 3D ? Réussira-t-il seulement à se faire une place sur ce marché où il est encore inexistant ?

Pendant ce temps, TSMC annonce être prêt à livrer des processeurs 28nm que les tablettes de 2012 devraient adopter en masse.

Une chose est sure, grâce au génie des chercheurs et ingénieurs, la loi de Moore a encore de beaux jours devant elle et la vie de geek restera palpitante encore quelques années !

article intéressent, mais la machine ARM est lancé a pleine vitesse alors que intel est encore au stand, il va falloir qu’ils arrivent a atteindre des records pour rattraper le marché qui leur échappe de plus en plus chaque jours.

D’autant plus que rien dit que ARM ne passera pas en tri-gate (ou autre procédé de gravure « évolué ») dans les prochaines années, ce qui réduira les efforts d’intel a néant.

http://www.comptoir-hardware.com/actus/processeurs/16091-seulement-12-milliard-de-transistors-dans-un-bulldozer-fx-8150-.html

;-)